# Towards a Practical Secure Concurrent Language

Stefan Muller and Stephen Chong

TR-05-12

Computer Science Group Harvard University Cambridge, Massachusetts

# Towards a Practical Secure Concurrent Language\*

Stefan Muller

Carnegie Mellon University smuller@cs.cmu.edu Stephen Chong Harvard University chong@seas.harvard.edu

# Abstract

We demonstrate that a practical concurrent language can be extended in a natural way with information security mechanisms that provably enforce strong information security guarantees. We extend the X10 concurrent programming language with coarse-grained information-flow control. Central to X10 concurrency abstractions is the notion of a *place*: a container for data and computation. We associate a security level with each place, and restrict each place to store only data appropriate for that security level. When places interact only with other places at the same security level, then our security mechanisms impose no restrictions. When places of differing security levels interact, our information security analysis prevents potentially dangerous information flows, including information flow through covert scheduling channels. The X10 concurrency mechanisms simplify reasoning about information flow in concurrent programs.

We present a static analysis that enforces a noninterference-based extensional information security condition in a calculus that captures the key aspects of X10's place abstraction and async-finish parallelism. We extend this security analysis to support many of X10's language features, and have implemented a prototype compiler for the resulting language.

*Categories and Subject Descriptors* D.3.3 [*Programming Languages*]: Language Constructs and Features—Concurrent programming structures; D.4.6 [*Operating Systems*]: Security and Protection—Information flow controls

*Keywords* Language-based security; information-flow control; X10.

## 1. Introduction

Enforcement of strong information security guarantees for concurrent programs poses both a challenge and an opportunity. The challenge is that, given current hardware trends towards increased parallelism, and the large number of computer systems that handle data of varying sensitivity, it is increasingly important to reason about and enforce information security guarantees in the presence of concurrency. Although progress has been made towards this end, there are not yet practical enforcement mechanisms and usable implementations. The opportunity is to adapt new and existing language abstractions for concurrency to reason precisely about information security in concurrent programs. Information security, like concurrency, is intimately connected to notions of dependency [1]. As such, there is potential for synergy between language mechanisms for concurrency, and enforcement mechanisms for information security in concurrent programs.

The X10 programming language [10] is an object-oriented language with abstractions to support fine-grained concurrency. Central to X10 concurrency abstractions is the notion of a place. A place is a computational unit that contains computation and data. For example, each core of a single machine or each machine within a distributed system might be represented by a different place. Data held at a place, and computation running at a place, are said to be "local" to the place. Places are first-class in X10. Multiple threads of execution, which in X10 are known as activities, may execute concurrently within a place. Activities at the same place share memory, and an activity may only access data at the place where it is located. Places may communicate using message passing, but X10 is designed to discourage excessive communication between places, since this reduces concurrency.

We extend X10 language abstractions for concurrency with information security mechanisms, and call the resulting language SX10 (for Secure X10). Specifically, in SX10 each place is associated with a security level, and a (completely static) security analysis ensures that each place stores only data appropriate for that security level. Thus, all computation within a place is on data at the same security level. In the case where places communicate only with other places at the same security level, then our security mechanisms do not impose any restrictions on programs. Communication between places with different security levels may pose security concerns, but because message-passing communication is used between places, it is relatively simple to restrict such communication: the security analysis ensures that data may be sent to another place only when the security level of the destination is sufficiently high. Interaction between places may

<sup>\*</sup> This technical report is an extended version of the paper of the same title that appeared in OOPSLA'12. This technical report provides additional proof details.

influence the scheduling of activities at a place, leading to potential covert information channels; our security analysis tracks and controls these covert channels.

We believe that this coarse-grained approach to providing information security in concurrent programs is simple, practical, and useful. All data at a place is at the same security level, which both provides simplicity of reasoning for the programmer, and allows a high degree of concurrency within a place without compromising security.

There are many highly concurrent systems that compute with data of varying sensitivity that fit naturally into such a model. The following are some examples.

- Machine learning A service such as Pandora processes a large amount of public data, which is then used to make recommendations to individual users based on their private usage data. All public data is at the same security level and processing it is highly parallel; data from many users are processed in parallel.

- Social networks Users specify that some posts are visible to all other users, and some are visible only to friends. Many users may use the system concurrently.

- **Shopping carts** An online shopping cart collects information about items ordered, which may appear in low-security logs, and credit card information, which must remain secure. Many customers may use the system concurrently.

*Motivating example* Reasoning about information security in the presence of concurrency can be subtle. Consider Program 1, which exhibits a timing channel.

```

1

at Low {

2

async {

// Activity 1

3

4

if (hi > 0) longComputation();

output "pos";

5

}

6

7

// Activity 2

mediumComputation(); output ''nonpos'';

8

9

```

| Program | 1. |

|---------|----|

|---------|----|

Assume that memory location hi contains high-security (e.g., secret) data. Instruction at Low s indicates that s is executed at a place called Low, which we assume is allowed to handle only low-security data. Outputs at place Low should not reveal high-security information. Instruction async s creates a new activity to execute statement s, and the current activity continues with the following statement. Thus, the if statement and subsequent output of the string "pos" execute concurrently with the output "nonpos" statement. If high-security memory location hi is positive, then Activity 1 outputs "pos" after a long time; otherwise it outputs "pos"

immediately. Activity 2 computes for a medium amount of time, and outputs ''nonpos''. It is likely that the order of outputs will reveal secret information, and the program is thus insecure. This is an example of an *internal timing channel* [47], where the order of publicly observable events depends upon high-security information.

Program 1 is not an SX10 program: low-security place Low is not allowed to hold high-security data, such as that stored in memory location hi. Suppose, however, that High is a place that is permitted to hold secret information. Then Program 2 is a SX10 program and exhibits a similar timing channel. (It is correctly rejected by our security analysis.)

| 1  | at Low {                                           |

|----|----------------------------------------------------|

| 2  | async {                                            |

| 3  | // Activity 1                                      |

| 4  | at High { // activity 1 moves to High              |

| 5  | if (hi > 0) longComputation();                     |

| 6  | }                                                  |

| 7  | // activity 1 moves back to Low                    |

| 8  | output ''pos'';                                    |

| 9  | }                                                  |

| 10 | // Activity 2                                      |

| 11 | <pre>mediumComputation(); output ''nonpos'';</pre> |

| 12 | }                                                  |

|    |                                                    |

Program 2.

In this example, Activity 1 moves to place High in order to perform computation on high-security data, before returning to place Low to perform the output of the string "pos".

We assume that the scheduling of activities at each place depends only on the activities at that place, an assumption that holds in the X10 2.2 runtime [14]. Nonetheless, in Program 2, the scheduling of Activity 2 at place Low depends on whether Activity 1 is running at Low, which in turn depends on how long the computation at place High takes. Thus, the scheduling of output "pos" and output "nonpos" may be influenced by high-security data. Our security analysis detects this potential information flow, and rejects the program.

Program 2 is inherently nondeterministic: it could perform the two outputs in either order. The scheduler resolves the nondeterminism, but in doing so, may reveal highsecurity information—a form of refinement attack [38]. One way to prevent such refinement attacks is to require that any observable behavior be deterministic [6, 48]. Our security analysis requires such observational determinism when the resolution of nondeterminism may reveal high-security information.

It is, however, possible to allow some observable nondeterminism within a secure concurrent program. Intuitively, if the resolution of the nondeterminism does not depend on high-security information, then observable nondeterminism is secure [30]. If place P does not communicate with any other places, then, since scheduling is performed perplace, resolution of nondeterminism at P will not reveal high-security information. In some cases it is also possible to allow nondeterminism at place P even if P interacts with places of higher security levels. Consider Program 3: Activity 1 executes at place Low concurrently with Activity 2's execution at place High. The finish s instruction executes statement s, and waits until s and all activities spawned by s have terminated before continuing execution. Thus, Activity 3 and Activity 4 execute concurrently at place Low after Activities 1 and 2 have finished. Although the order of output "B" and output "C" is nondeterministic, resolution of this nondeterminism is not influenced by how long the high-security computation takes, and so does not reveal high-security information.

```

1

at Low {

2

finish {

async {

3

// Activity 1

4

output "'A'';

5

6

7

// Activity 2

at High {

8

if (hi > 0) longComputation();

9

10

}

}

11

async {

12

// Activity 3

13

14

output "B";

15

// Activity 4

16

output "C";

17

18

```

| Due ana | 2  |

|---------|----|

| Program | э. |

**Contributions** The key contribution of this paper is to demonstrate that practical and useful concurrency mechanisms can be extended in a natural way with information security mechanisms that provably enforce strong information flow control [38], requiring that every place can store only data at a single security level. If places interact only with other places at the same security level, then our security mechanisms do not restrict concurrency nor require determinism for security. When places of differing security interact, our information flows by using X10's concurrency mechanisms to reason both about data sent between places, and about how the scheduling of activities at a place may depend on high-security information.

In Section 2 we present a calculus, based on Featherweight X10 [22], that captures key aspects of the X10 place abstraction, and its async-finish parallelism. We define a knowledge-based noninterference semantic security condition [2, 12] for this calculus in Section 3, and present a security analysis that provably enforces it. The language SX10 is the result of extending this analysis to handle many of the language features of X10. We have implemented a prototype compiler for SX10 by modifying the X10 compiler, and this is described in Section 4. We discuss related work in Section 5 and conclude in Section 6.

## 2. FSX10: a secure parallel calculus

In this section, we introduce the calculus FSX10, based on Featherweight X10 [22]. Like Featherweight X10, this calculus captures X10's async-finish parallelism, but adds places and interaction with the external environment via input and output instructions.

#### 2.1 Syntax

The abstract syntax of FSX10 is presented in Figure 1. A *place* P is a container for data and activities. In FSX10, as in X10, every memory location r and every activity is associated with a place. In FSX10, however, places are simply identifiers and are not first-class values. Function  $Place(\cdot)$  describes how memory locations are mapped to places: memory location r is held at place Place(r), and only code executing at that place is allowed to access the location.

For simplicity, we restrict values in the calculus to integers. Expressions e consist of integer constants v, variables x, memory reads !r (where r is a memory location), and total binary operations over expressions  $e_1 \oplus e_2$ .

Statements s are sequences of instructions. Every instruction is labeled with a program point. For example, a store instruction  $r :=^{p} e$  has program point p. For convenience we write  $s^{p}$  to indicate that program point p is the program point of the first instruction of statement s. When the program point of an instruction is irrelevant, we omit it.

Instructions include no-ops (skip), selection (if e then s else s), and iteration (while e do s). Instruction r := e evaluates expression e and updates memory location r with the result. Instruction let x = e in s evaluates expression e to a value, and uses that value in place of variable x in the evaluation of statement s. Once defined, variable x is immutable. A variable defined at place P may be used at a different place P', which can be thought of as P sending the value of the variable to P'.

Instruction async s creates a new activity that starts executing statement s, and the current activity continues executing the next instruction. Instruction at P s executes statement s at place P. Note that at Ps does not create a new activity: execution of the next instruction waits until s has terminated. That is, given the statement at P s; r := 42; skip, the assignment of 42 to memory location r will not occur until after statement s has finished execution. Instruction backat Ps does not appear in source programs, but is used by the operational semantics to track when control will return back to place P as a result of finishing an at P' s' instruction. Finally, instruction finish s will block until statement s, and all activities created by s, have terminated.

## Metavariables

- *P* ranges over places

- p ranges over program points

- v ranges over integer constants

- x ranges over program variables

- r ranges over memory locations

- $\oplus$  ranges over total binary integer functions

Expressions

| e | ::= | v            | Integer constant |

|---|-----|--------------|------------------|

|   |     | x            | Variable         |

|   |     | !r           | Memory read      |

|   | Ì   | $e \oplus e$ | Binary operation |

|   |     |              |                  |

No-op Sequence

Statements

| s | ::= | $skip^p$ |

|---|-----|----------|

|   |     | i;s      |

Instructions

|       | i | ::= | $skip^p$                                               | No-op        |

|-------|---|-----|--------------------------------------------------------|--------------|

|       |   |     | $r :=^p e$                                             | Memory write |

|       |   |     | $if^p \ e \ then \ s \ else \ s$                       | Conditional  |

|       |   |     | $while^p  e  do  s$                                    | Iteration    |

|       |   |     | $\operatorname{let}^p x = e \operatorname{in} s$       | Let          |

|       |   |     | $\operatorname{output}^p e$                            | Output       |

|       |   |     | $input^p r$                                            | Input        |

|       |   |     | $\operatorname{async}^p s$                             | Asynchronous |

|       |   |     | $\operatorname{at}^p Ps$                               | At           |

|       |   |     | $finish^p s$                                           | Finish       |

|       |   |     | $backat^p P$                                           | Back at      |

| Trees |   | ::= | $\langle P, s \rangle$                                 | Activity     |

|       |   |     | $T \parallel T$                                        | Parallel     |

|       |   |     | $T \stackrel{''}{\triangleright} \langle P, s \rangle$ | Join         |

|       |   | ĺ   | $\checkmark$                                           | Done         |

|       |   |     |                                                        |              |

| Figure 1. | FSX10 | syntax |

|-----------|-------|--------|

|-----------|-------|--------|

FSX10 programs can communicate with the external environment via input and output instructions. We assume, without loss of generality, that every place has a single communication channel. Instruction output e, when executed at place P, will evaluate expression e to a value, and output that value on P's channel. Similarly, instruction input r, when executed at P, will input a value from P's channel, and store the result in location r. We assume that there is always data available for input on a channel, and thus input instructions are non-blocking.

Concurrently executing activities in FSX10 are represented using *trees*. Tree  $\langle P, s \rangle$  is an activity at place P executing statement s. Tree  $T_1 || T_2$  represents trees  $T_1$  and  $T_2$  executing concurrently. Tree  $\checkmark$  indicates a terminated activity, and tree  $T \triangleright \langle P, s \rangle$  indicates that activity  $\langle P, s \rangle$  is blocked until all activities in T have terminated.

## 2.2 Events, traces, and input strategies

As a program executes, it generates input and output events. Input event i(v, P) is generated when an input instruction accepts value v from P's channel. Output event o(v, P) is generated when an output instruction outputs value v on P's channel.

A *trace* t is a (possibly empty) sequence of input, output and location assignment events. Other events are not tracked. We write  $\epsilon$  for the empty trace. We write  $t|_P$  for the subsequence of events of t that occur at place P. More formally, we have

$$\epsilon \upharpoonright_P = \epsilon$$

$$(t \cdot \alpha) \upharpoonright_P = \begin{cases} (t \upharpoonright_P) \cdot \alpha & \text{if } Place(\alpha) = P\\ t \upharpoonright_P & \text{otherwise} \end{cases}$$

where function  $Place(\alpha)$  is the place at which  $\alpha$  occurred:

$$Place(i(v, P)) = P$$

$Place(o(v, P)) = P.$

We model input from the external environment with *input* strategies [30]. Input strategy  $\omega$  is a function from places and traces to values, such that given trace t, value  $\omega(P, t \upharpoonright_P)$  is the next value to input on the channel for P. Note that the choice of the next value that will be input on a channel can depend on the previous outputs of the channel. In Section 3, where we consider the security of FSX10 programs, we will be concerned with ensuring that low-security attackers are unable to learn about the inputs to high-security places.

#### 2.3 Scheduling

Since program execution, and information security, depends on scheduling, we model the scheduler in FSX10. We explicitly refine the nondeterminism inherent in scheduling using *refiners* [30] to represent the decisions made by the scheduler. Essentially, all nondeterminism in program execution is encapsulated in a refiner; once a refiner has been chosen, program execution is deterministic.

In X10, a place represents a distinct computational node with a distinct scheduler [14]. In accordance with this model, we assume that scheduling decisions are made on a per-place basis, and the choice of which activity to run at a given place depends only on the set of activities currently executing at that place.

We model these assumptions by representing a refiner R as a pair (Ps, Sch), where Ps is a stream of places indicating the order in which places take steps, and Sch is a function from places to streams chs of *scheduling functions*. A scheduling function ch takes a set of program points (representing the set of activities currently executing at the

PLACE

$$Sch(P) = chs \cdot ch \qquad \text{PointsRunning}(T, P) \neq \emptyset \qquad \text{IDLEPLACE} \\ \frac{ch(\text{PointsRunning}(T, P)) = p}{(H; \omega; t; T) \xrightarrow{p} (H'; \omega; t'; T')} \qquad \frac{(H; \omega; (P \cdot Ps, Sch); t; T) \rightarrow (H'; \omega; (Ps, Sch[P \rightarrow chs]); t'; T')}{(H; \omega; (P \cdot Ps, Sch); t; T) \rightarrow (H'; \omega; (Ps, Sch); t; T)} \qquad \frac{(H; \omega; (P \cdot Ps, Sch); t; T) \rightarrow (H; \omega; (Ps, Sch); t; T)}{(H; \omega; (Ps, Sch); t; T) \rightarrow (H; \omega; (Ps, Sch); t; T)}$$

PointsRunning

$$(\checkmark, P) = \emptyset$$

PointsRunning $(\langle P', s^p \rangle, P) = \begin{cases} \{p\} & \text{if } P' = P \\ \emptyset & \text{if } P' \neq P \end{cases}$

PointsRunning $(T_1 || T_2, P) = \text{PointsRunning}(T_1, P) \cup \text{PointsRunning}(T_2, P)$

PointsRunning $(T \triangleright \langle P', s \rangle, P) = \text{PointsRunning}(T, P)$

**Figure 2.** Program semantics  $(H; \omega; R; t; T) \rightarrow (H'; \omega; R'; t'; T')$

place), and returns an element of that set (representing which of the activities should be scheduled). We write  $P \cdot Ps$  for a stream with first element P and remaining elements Ps.

Thus, if the refiner is  $(P \cdot Ps, Sch)$ , then place P will take a step next, and if  $Sch(P) = ch \cdot chs$  (where ch is the first element of the stream of scheduling function, and chs is the remainder of the stream), then scheduling function ch will be used to determine which of the current activities at P will be scheduled. Note that each time a place takes a step, it may use a different scheduling function. However, the sequence of scheduling functions at a given place must be decided in advance, and may not depend on the history of computation at the place.

The use of a stream of scheduling functions per place allows our model to capture many realistic scheduling algorithms, such as round robin, shortest remaining time, and fixed priority. Scheduling algorithms that depend on the history of computation at a place (such as the work-stealing scheduling algorithm used in the X10 runtime [14, 15]) cannot be directly represented in this model. However, we believe the security guarantees still hold for the X10 runtime; we further discuss the security of the X10 scheduler in Section 4.

#### 2.4 Operational semantics

A program configuration is a 5-tuple  $(H; \omega; R; t; T)$ . Heap H maps locations r to values, and is updated as the program executes. Input strategy  $\omega$  is used to determine values input on channels; the input strategy does not change during execution, but we include it in the program configuration for notational convenience. Refiner R is used to determine scheduling, and is updated during execution. Trace t is the trace (of input, output, and location assignment events) produced so far by the program's execution. Tree T is the tree of currently executing activities.

The small-step operational semantics relation

$$(H;\omega;R;t;T) \to (H';\omega;R';t';T')$$

| Const   | Read                                                           |

|---------|----------------------------------------------------------------|

|         | H(r) = v $Place(r) = P$                                        |

| P; H; u | $\overrightarrow{v \Downarrow v} \qquad P; H; !r \Downarrow v$ |

|         |                                                                |

|         | Ор                                                             |

|         | $P; H; e_1 \Downarrow v_1 \qquad P; H; e_2 \Downarrow v_2$     |

|         | $P; H; e_1 \oplus e_2 \Downarrow v_1 \oplus v_2$               |

| <b>Figure 4.</b> Expression semantics $P; H; e \downarrow$ | pression semantics $P; H; e \Downarrow v$ | gure 4. Expression | Figure 4. |

|------------------------------------------------------------|-------------------------------------------|--------------------|-----------|

|------------------------------------------------------------|-------------------------------------------|--------------------|-----------|

describes how a program configuration changes as a result of execution. Due to the use of refiners, the operational semantics is deterministic. Inference rules for this relation are given in Figure 2.

Rule PLACE uses the refiner to select a place P to execute, and to select a scheduling function ch to schedule an activity at P. Set PointsRunning(T, P) is the set of program points of running activities located at P (also defined in Figure 2), which is given to scheduling function ch to select an activity. Rule IDLEPLACE handles the case where the refiner has selected place P to execute, but P does not have any currently running activities. Judgment

$$(H; \omega; t; T) \xrightarrow{p} (H'; \omega; t'; T')$$

is used to indicate that tree configuration  $(H; \omega; t; T)$  executes the instruction at program point p to produce tree configuration  $(H'; \omega; t'; T')$ . Tree configurations are similar to program configurations, but omit the refiner, since the refiner is used only to determine which activity to execute.

Inference rules for  $(H; \omega; t; T) \xrightarrow{p} (H'; \omega; t'; T')$  are given in Figure 3. Rules PARALEFT, PARARIGHT, PAR-ALEFTDONE, PARARIGHTDONE, JOIN, and JOINDONE navigate through the tree structure to find the appropriate activity to execute. Rule SKIP1 reduces a skip statement to a terminated activity  $\checkmark$ . The remaining rules execute a single instruction.

Several of the rules for evaluating instructions evaluate expressions to values, using judgment  $P; H; e \Downarrow v$ , which

| PARALEFT                                                                                                                                                                                        | PARARIGHT                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{(H; \omega; t; T_1) \xrightarrow{p} (H'; \omega; t'; T_1') \qquad T_1' \neq \checkmark}{(H; \omega; t; T_1    T_2) \xrightarrow{p} (H'; \omega; t'; T_1'    T_2)}$                       | $(H;\omega;t;T_2) \xrightarrow{p} (H';\omega;t';T_2') \qquad T_2' \neq \checkmark$                                                                                                                            |

| $(H; \omega; t; T_1    T_2) \xrightarrow{p} (H'; \omega; t'; T_1'    T_2)$                                                                                                                      | $\frac{(H;\omega;t;T_2) \xrightarrow{p} (H';\omega;t';T_2') \qquad T_2' \neq \checkmark}{(H;\omega;t;T_1 \mid\mid T_2) \xrightarrow{p} (H';\omega;t';T_1 \mid\mid T_2')}$                                     |

| ParaLeftDone                                                                                                                                                                                    | ParaRightDone                                                                                                                                                                                                 |

| $\frac{(H;\omega;t;T_1) \xrightarrow{p} (H';\omega;t';\checkmark)}{(H;\omega;t;T_1 \mid\mid T_2) \xrightarrow{p} (H';\omega;t';T_2)}$                                                           | $\frac{(H;\omega;t;T_2)\xrightarrow{p}(H';\omega;t';\checkmark)}{(H;\omega;t;T_1  T_2)\xrightarrow{p}(H';\omega;t';T_1)}$                                                                                     |

| $(H; \omega; t; T_1    T_2) \xrightarrow{p} (H'; \omega; t'; T_2)$                                                                                                                              | $(H;\omega;t;T_1  T_2)\xrightarrow{p}(H';\omega;t';T_1)$                                                                                                                                                      |

| Join                                                                                                                                                                                            | JoinDone                                                                                                                                                                                                      |

| $\frac{(H;\omega;t;T)\xrightarrow{p}(H';\omega;t';T') \qquad T'\neq\checkmark}{(H;\omega;t;T\triangleright\langle P,s\rangle)\xrightarrow{p}(H';\omega;t';T'\triangleright\langle P,s\rangle)}$ | $\frac{(H;\omega;t;T)\xrightarrow{p}(H';\omega;t';\checkmark)}{(H;\omega;t;T\triangleright\langle P,s\rangle)\xrightarrow{p}(H';\omega;t';\langle P,s\rangle)}$                                               |

| $(H;\omega;t;T \triangleright \langle P,s \rangle) \xrightarrow{p} (H';\omega;t';T' \triangleright \langle P,s \rangle)$                                                                        | $(H;\omega;t;T \triangleright \langle P,s\rangle) \xrightarrow{p} (H';\omega;t';\langle P,s\rangle)$                                                                                                          |

| Skip1                                                                                                                                                                                           | Skip2                                                                                                                                                                                                         |

| $(H;\omega;t;\langle P,skip^p\rangle) \xrightarrow{p} (H;\omega;t;\checkmark)$                                                                                                                  | $(H;\omega;t;\langle P,skip^p;s\rangle) \xrightarrow{p} (H;\omega;t;\langle P,s\rangle)$                                                                                                                      |

| WRITE                                                                                                                                                                                           | Let                                                                                                                                                                                                           |

| $\begin{array}{c} P;H;e \Downarrow v  Place(r) = P\\ \hline (H;\omega;t;\langle P,r:=^{p}e;s\rangle) \xrightarrow{p} (H[r\mapsto v];\omega;t;\langle P,s\rangle) \end{array}$                   | $\frac{P; H; e \Downarrow v \qquad s_1' = s_1\{v/x\}}{(H; \omega; t; \langle P, let^p x = e in s_1; s_2 \rangle) \xrightarrow{p} (H; \omega; t; \langle P, s_1' \bullet s_2 \rangle)}$                        |

| $(H; \omega; t; \langle P, r :=^{p} e; s \rangle) \xrightarrow{P} (H[r \mapsto v]; \omega; t; \langle P, s \rangle)$                                                                            | $(H; \omega; t; \langle P, let^p x = e in  s_1; s_2 \rangle) \xrightarrow{P} (H; \omega; t; \langle P, s_1' \bullet s_2 \rangle)$                                                                             |

| Async                                                                                                                                                                                           | Finish                                                                                                                                                                                                        |

| $(H; \omega; t; \langle P, async^p s_1; s_2 \rangle) \xrightarrow{p} (H; \omega; t; \langle P, s_1 \rangle    \langle P, s_2 \rangle)$                                                          | $(H; \omega; t; \langle P, finish^p s_1; s_2 \rangle) \xrightarrow{p} (H; \omega; t; \langle P, s_1 \rangle \triangleright \langle P, s_2 \rangle)$                                                           |

| AT                                                                                                                                                                                              | BackAt                                                                                                                                                                                                        |

| $(H; \omega; t; \langle P_1, at^p P_2 s_1; s_2 \rangle) \xrightarrow{p} (H; \omega; t; \langle P_2, s_1 \bullet (backat))$                                                                      | $P_1;s_2)\rangle) \qquad (H;\omega;t;\langle P_2,backat^pP_1;s\rangle) \xrightarrow{p} (H;\omega;t;\langle P_1,s\rangle)$                                                                                     |

| Dutput                                                                                                                                                                                          | Input                                                                                                                                                                                                         |

| $P; H; e \Downarrow v$                                                                                                                                                                          | $\begin{array}{c} Place(r) = P \qquad \omega(P,t\restriction_P) = v \\ \hline (H;\omega;t;\langle P,input^pr;s\rangle) \xrightarrow{p} (H[r\mapsto v];\omega;t\cdot i(v,P);\langle P,s\rangle) \end{array}$   |

| $(H; \omega; t; \langle P, output^p e; s \rangle) \xrightarrow{p} (H; \omega; t \cdot o(v, P); \langle P, s \rangle)$                                                                           | $(H; \omega; t; \langle P, input^p  r; s \rangle) \xrightarrow{p} (H[r \mapsto v]; \omega; t \cdot i(v, P); \langle P, s \rangle)$                                                                            |

| 1                                                                                                                                                                                               | IF2                                                                                                                                                                                                           |

| $P; H; e \Downarrow v \qquad v \neq 0$                                                                                                                                                          | $P; H; e \Downarrow v \qquad v = 0$ $(H; \omega; t; \langle P, if^{p} e \text{ then } s_{1} \text{ else } s_{2}; s_{3} \rangle) \xrightarrow{p} (H; \omega; t; \langle P, s_{2} \bullet s_{3} \bullet s_{3})$ |

| $H; \omega; t; \langle P, if^{P} e then s_1 else s_2; s_3 \rangle) \to \langle H; \omega; t; \langle P, s_1 \bullet s_3 \rangle$                                                                | ( <i>H</i> ; $\omega$ ; <i>t</i> ; $\langle P, if^{P} e then s_1 else s_2; s_3 \rangle$ ) $\rightarrow$ ( <i>H</i> ; $\omega$ ; <i>t</i> ; $\langle P, s_2 \bullet s_3 \rangle$ )                             |

| WHILE                                                                                                                                                                                           |                                                                                                                                                                                                               |

| $(H;\omega;t;\langle P,(while^pedos_1);s_2\rangle)\stackrel{p}{\twoheadrightarrow}(H;\omega;t)$                                                                                                 | $t; \langle P, (if e then (s_1 \bullet while e do s_1; skip) else skip); s_2 \rangle)$                                                                                                                        |

|                                                                                                                                                                                                 | $(\mathbf{T}, \mathbf{r})^p$                                                                                                                                                                                  |

PARARIGHT

PARALEFT

**Figure 3.** Tree and statement semantics  $(H; \omega; t; T) \xrightarrow{p} (H'; \omega; t'; T')$

is defined in Figure 4. Evaluation of expressions is standard, with the exception of memory read !r, which requires that memory location r is held at place P, the current place of the activity performing the read.

Rule SKIP2 handles the instruction skip—it is a no-op. Rule WRITE executes write instruction  $r :=^{p} e$  by evaluating expression e to a value v and updating the heap to map location r to v. Note that location r must be stored at the place at which the activity is executing: Place(r) = P.

Rule LET executes let instruction let x = e in s by evaluating expression e to value v, and substituting uses of variable x in s with v using capture-avoiding substitution  $s\{v/x\}$ . The rule uses the operation  $\bullet$  to "stitch together" two statements into a single statement. This operation is defined recursively as follows.

$$\begin{split} (i;s_1) \bullet s_2 &= i; (s_1 \bullet s_2) \\ \mathrm{skip} \bullet s_2 &= s_2 \end{split}$$

Instruction async  $s_1$  creates a new activity to execute  $s_1$ , and the current activity continues with the next statement. Thus, rule ASYNC executes the activity  $\langle P, async s_1; s_2 \rangle$  by reducing it to the tree  $\langle P, s_1 \rangle || \langle P, s_2 \rangle$ .

Statement finish  $s_1$ ;  $s_2$  executes  $s_1$ , and waits until all activities spawned by  $s_1$  have terminated before executing  $s_2$ . Rule FINISH transforms activity  $\langle P$ , finish  $s_1$ ;  $s_2 \rangle$  to the tree  $\langle P, s_1 \rangle \triangleright \langle P, s_2 \rangle$ .

Statement at  $P s_1$ ;  $s_2$  executes statement  $s_1$  at place P, and then executes  $s_2$  at the original place. Rule AT thus transforms activity  $\langle P', \text{at } P s_1; s_2 \rangle$  to an activity at place P:  $\langle P, s_1 \bullet (\text{backat } P'; s_2) \rangle$ . We insert the instruction backat P'to let us know both that execution of  $s_2$  will be at place P', and that the movement of the activity to P' is the result of returning from a previous at instruction. Rule BACKAT for statement backat P' simply changes the place of the activity back to place P'.

Rule OUTPUT evaluates output instruction output e by evaluating e to value v, and appending event o(v, P) to the program's trace, where P is the current place of the activity. Similarly, rule INPUT evaluates input instruction input rby inputting value v from P's communication channel, updating the heap to map location r to v, and appending event i(v, P) to the program's trace. The value to input is determined by input strategy  $\omega$ , and is equal to  $\omega(P, t|_P)$ , where P is the current place of the activity, and  $t|_P$  is the program's trace so far restricted to events occurring at place P.

Rules IF1 and IF2 handle the conditional instruction if e then  $s_1$  else  $s_2$  by reducing it to  $s_1$  if e evaluates to a nonzero value, and reducing it to  $s_2$  otherwise. Rule WHILE handles a while e do  $s_1$  instruction by unrolling it into a conditional instruction.

## 2.5 Program execution

A program is an activity  $\langle P, s \rangle$ , that is, a statement s that is intended to start execution at place P. Program execution depends on an input strategy  $\omega$  and a refiner R. The initial configuration of a program is  $(H_{init}; \omega; R; \epsilon; \langle P, s \rangle)$ , where  $H_{init}$  is a distinguished heap and  $\epsilon$  is the empty trace.

For program  $\langle P, s \rangle$ , input strategy  $\omega$ , and refiner R, we write

$$(\langle P, s \rangle, \omega, R)$$

emits t

to indicate that program execution can produce trace t. That is, there is some heap H', refiner R' and tree T' such that

$$(H_{init};\omega;R;\epsilon;\langle P,s\rangle) \rightarrow^* (H';\omega;R';t;T')$$

where  $\rightarrow^*$  is the reflexive transitive closure of the small-step relation  $\rightarrow$ .

## 3. Security

We are interested in enforcing strong information security in concurrent programs. Towards that end, in this section, we define a noninterference-based [12] definition of security for FSX10, and present a type system that enforces security while allowing many useful and highly concurrent programs.

#### 3.1 Defining security

Intuitively, we want to ensure that a consumer of lowsecurity information from a FSX10 program does not learn anything about high-security information. In our setting, consumers of low-security information are entities that can observe the communication channel of low-security places, and the high-security information that needs to be protected are the values input at high-security places.

We assume that there is a set of security levels  $\mathcal{L}$  with a partial order  $\sqsubseteq$  that describes relative restrictiveness of the security levels. We further assume that every place P is associated with a security level, denoted  $\mathcal{L}(P)$ . Intuitively, place P will be allowed to store and handle only data of security level  $\mathcal{L}(P)$  and lower, and to send values to, and invoke code on, only places P' such that  $\mathcal{L}(P) \sqsubseteq \mathcal{L}(P')$ .

For a given security level  $\ell \in \mathcal{L}$ , a *low-security place* is any place P such that the level of the place is less than or equal to  $\ell$ , that is,  $\mathcal{L}(P) \sqsubseteq \ell$ . All other places are *highsecurity places*, i.e., P is a high-security place if  $\mathcal{L}(P) \not\sqsubseteq \ell$ .

We define a semantic security condition based on *at*tacker knowledge [2]. An attacker observes the communication channels of low-security places. The knowledge of an attacker is the set of input strategies that are consistent with the attacker's observations: the smaller the set, the more accurate the attacker's knowledge. The semantic security condition will require that at all times, the attacker's knowledge includes all possible input strategies for high-security places. That is, all possible input strategies for high-security places are consistent with the attacker's observations. For ease of presentation, we will use a slightly weaker semantic security condition, a *progress-insensitive* condition [3] that also allows the attacker to learn not only the input strategies for low security places, but also whether low-security output is produced. **Trace equivalence** Given an attacker with security level  $\ell \in \mathcal{L}$  (i.e., who can observe communication channels of places P such that  $\mathcal{L}(P) \sqsubseteq \ell$ ), two executions of a program look the same to the attacker if the trace of inputs and outputs at low-security places are the same in both executions. We define this formally via  $\ell$ -equivalence of traces.

**Definition 1** ( $\ell$ -equivalence of traces). Let  $\ell \in \mathcal{L}$ . Traces  $t_0$  and  $t_1$  are  $\ell$ -equivalent, written  $t_0 \sim_{\ell} t_1$ , if  $t_0 \upharpoonright_{\ell} = t_1 \upharpoonright_{\ell}$ , where

$$\epsilon \restriction_{\ell} = \epsilon$$

$$(t \cdot \alpha) \restriction_{\ell} = \begin{cases} (t \restriction_{\ell}) \cdot \alpha & \text{if } \mathcal{L}(Place(\alpha)) \sqsubseteq \ell \\ t \restriction_{\ell} & \text{otherwise} \end{cases}$$

Attacker knowledge For a given execution of a program, starting from program configuration  $(H_{init}; \omega; R; \epsilon; \langle P, s \rangle)$ , that produces trace t, the knowledge of an attacker with security level  $\ell$ , written  $k(\langle P, s \rangle, R, t, \ell)$ , is the set of input strategies that could have produced a trace that is equivalent to what the attacker observed.

**Definition 2** (Attacker knowledge). For any  $\ell \in \mathcal{L}$ , program  $\langle P, s \rangle$ , trace *t*, and refiner *R*, the attacker's knowledge is:

$$\begin{split} k(\langle P,s\rangle,R,t,\ell) = \\ \{\omega \mid \exists t'. \; (\langle P,s\rangle,\omega,R) \text{ emits } t' \wedge t \sim_{\ell} t'\} \end{split}$$

We define what information an attacker with security level  $\ell$  is permitted to learn about input strategies by defining  $\ell$ -equivalence of input strategies. Intuitively, if two strategies are  $\ell$ -equivalent, then they provide the exact same inputs for all low-security places, and an attacker with security level  $\ell$  should not be able to distinguish them.

**Definition 3** ( $\ell$ -equivalence of input strategies). Let  $\ell \in \mathcal{L}$ . Input strategies  $\omega_0$  and  $\omega_1$  are  $\ell$ -equivalent, written  $\omega_0 \sim_{\ell} \omega_1$ , if for all places P such that  $\mathcal{L}(P) \sqsubseteq \ell$ , and for all traces t, we have  $\omega_0(P, t \upharpoonright_P) = \omega_1(P, t \upharpoonright_P)$ .

Relation  $\sim_{\ell}$  is an equivalence relation, and we write  $[\omega]_{\ell}$  for the equivalence class of  $\omega$  under the relation  $\sim_{\ell}$ .

Given a program configuration  $(H_{init}; \omega; R; \epsilon; \langle P, s \rangle)$ that produces trace t, progress knowledge [3] is the set of input strategies that could have produced a trace that is  $\ell$ equivalent to t, and could produce at least one more observable event. We will use progress knowledge as a lower bound on the allowed knowledge of an attacker. That is, we will explicitly allow the attacker to learn whether a program will produce another observable event. This means that the attacker may be permitted to learn the termination behavior of statements that depend on high-security information. **Definition 4** (Progress knowledge). For any  $\ell \in \mathcal{L}$ , program  $\langle P, s \rangle$ , trace *t*, and refiner *R*, progress knowledge is:

$$\begin{aligned} k^+(\langle P, s \rangle, R, t, \ell) &= \\ \{\omega \mid \exists t', \alpha. \ (\langle P, s \rangle, \omega, R) \text{ emits } (t' \cdot \alpha) \\ &\wedge t \sim_{\ell} t' \wedge \mathcal{L}(Place(\alpha)) \sqsubseteq \ell \} \end{aligned}$$

Our security condition requires that, for all attackers, and all executions, for each event the attacker can observe, the attacker learns no more than the input strategy for lowsecurity places, and the fact that another event was produced.

**Definition 5** (Security). Program  $\langle P, s \rangle$  is secure if for all  $\ell \in \mathcal{L}$ , traces  $t \cdot \alpha$ , refiners R, and input strategies  $\omega$  such that

$$(\langle P, s \rangle, \omega, R)$$

emits  $(t \cdot \alpha)$

we have

$$k(\langle P, s \rangle, R, t \cdot \alpha, \ell) \quad \supseteq \quad [\omega]_{\ell} \cap k^+(\langle P, s \rangle, R, t, \ell).$$

Recall that the attacker's knowledge is set of input strategies that are consistent with the attacker's observations: a smaller set means more precise knowledge. Security requires that there are lower bounds to the precision of the attacker's knowledge. That is, there is information that the attacker is not permitted to learn. Thus, security requires that attacker's knowledge is a superset of the knowledge it is permitted to learn.

According to this definition of security, Program 2 from the Introduction is insecure (assuming that memory location hi is initialized from an input from place High), since there exists a refiner and a strategy that will produce a trace that allows an observer of low-security outputs to learn something about the high-security input strategy. Indeed, our definition of security rules out internal timing channels [47], in which the order of low-security events (here, input, output, and accesses to memory locations) depends upon highsecurity information. Program 3 does not exhibit an internal timing channel, and is secure.

This definition of security is *progress insensitive* [3], as it permits the attacker to learn that program execution makes progress, and produces another observable output. This definition can be strengthened in a straightforward way to a *progress sensitive* security condition. While the type system of Section 3.2 enforces progress insensitive security, it can be modified using standard techniques (to conservatively reason about termination of loops) to enforce progress sensitive security [28]. We refrain from doing so to simplify the presentation of the type system.

#### 3.2 Enforcing security

We enforce security using a security type system. The type system ensures that each place P stores and handles only data input from places P' such that  $\mathcal{L}(P') \sqsubseteq \mathcal{L}(P)$ . However, as noted in the Introduction, it is possible for the

scheduling of activities at place P to be influenced by input from a place P' such that  $\mathcal{L}(P') \not\subseteq \mathcal{L}(P)$ . Our type system tracks and controls information flow through this covert channel through program point contexts.

A program point context  $\Delta$  is a function from program points to security levels such that  $\Delta(p)$  is an upper bound on the level of information that may influence the scheduling of program point p. More precisely, it is an upper bound on information that may affect the presence or absence of activities that may run concurrently with p at the same place.

Each program point is statically associated with a place, and we write Place(p) for the place at which program point p will execute. Intuitively, since program point p is executed at place Place(p), and Place(p) handles data at security level  $\mathcal{L}(Place(p))$ , we would expect that  $\Delta(p)$  is at least as restrictive as  $\mathcal{L}(Place(p))$ . Indeed, the type system ensures for all p that  $\mathcal{L}(Place(p)) \sqsubseteq \Delta(p)$ .

It is often the case that  $\mathcal{L}(Place(p))$  is also an upper bound of  $\Delta(p)$ . That is, the scheduling of p does not depend on any high-security information. However, if p may happen immediately after a computation at a high-security place finishes (as with the output "pos" instruction in Program 2), or in parallel with another program point at the same place whose scheduling depends on high-security information, then it is possible that  $\Delta(p) \not\subseteq \mathcal{L}(Place(p))$ . In that case, in order to ensure that the scheduling decision at place Place(p) does not leak high-security information, we require observational determinism [48] at Place(p) during the scheduling of p. That is, for each memory location stored at Place(p), there are no data races on that location, and the order of input and output at Place(p) is determined.

Finally, variable context  $\Gamma$  maps program variables to the place at which the variable was created. The type system uses the variable context to ensure that if variable x was declared at place P, then x is used only at places P' such that  $\mathcal{L}(P) \sqsubseteq \mathcal{L}(P')$ .

**May-happen-in-parallel analysis** The type system relies on the results of a may-happen-in-parallel analysis, such as the one presented by Lee and Palsberg for Featherweight X10 [22]. The async-finish parallelism of X10 is amenable to a precise may-happen-in-parallel analysis. We write MHPP(p) for the set of program points that may happen in parallel with program point p at the same place (i.e., at Place(p)).

**Typing expressions** Judgment  $p; \Gamma; \Delta \vdash e$  indicates that expression e, occurring at program point p is well typed under variable context  $\Gamma$  and program point context  $\Delta$ . Inference rules for this judgment are given in Figure 5. Constants v are always well typed, and the use of variable x is well typed if the level of the place at which x is defined  $(\mathcal{L}(\Gamma(x)))$  is less than or equal to the level of the place at which x is used  $(\mathcal{L}(Place(p)))$ . Expression  $e_1 \oplus e_2$  is well typed if both  $e_1$  and  $e_2$  are well typed.

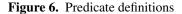

$noWrite(r, p) = \forall p' \in \mathsf{MHPP}(p).$  instruction at p' does not write to r

$$\begin{split} noReadWrite(r,p) &= noWrite(r,p) \ \land \\ \forall p' \in \mathsf{MHPP}(p). \text{ instruction at} \\ p' \text{ does not read } r. \end{split}$$

$noIO(p) = \forall p' \in \mathsf{MHPP}(p).$  instruction at p'does not perform input or output.

There are two different rules for reading memory location r. The first rule, rule T-READNONDET, handles the case where the scheduling of the expression's execution at place Place(p) is influenced by information at most at level  $\mathcal{L}(Place(p))$ . In that case, there are no restrictions on when the read may occur: it may occur concurrently with activities at the same place that write to the location since the resolution of the data race will not be a covert information channel. (The existence of a data race may, however, be undesirable in terms of program functionality.)

The second rule, rule T-READDET, applies when the scheduling of the expression may be influenced by information that is not allowed to flow to level  $\mathcal{L}(Place(p))$ . In that case, the read is required to be observationally deterministic: predicate noWrite(r, p) must hold, implying that the read of memory location r at program point p must not execute concurrently with any statement that may write to r. Predicate noWrite(r, p) is defined in Figure 6.

**Typing statements** Judgment  $\Gamma; \Delta \vdash s : \ell$  indicates that statement *s* is well typed in variable context  $\Gamma$  and program point context  $\Delta$ , and that security level  $\ell$  is an upper bound on the security level of information that may influence the scheduling of the last program point of *s*. Inference rules for the judgment are given in Figure 7.

Every inference rule for a statement  $s^p$  includes the premise  $\forall p' \in \mathsf{MHPA}(p)$ .  $\Delta(p') \sqsubseteq \Delta(p)$ . Intuitively, the set MHPA(p) is the set of program points that may influence the presence or absence of activities running in parallel with p at the same place. Assuming that Place(p) = P, MHPA(p) contains the program points of backat P instructions that may happen in parallel with p, and the set of program points immediately following an  $at^{p'} P' s'$  instruction, where Place(p') = P and p' may happen in parallel with p. The set MHPA(p) is a subset of the program points that may happen in parallel with p, and can easily be computed from the results of a may-happen-in-parallel analysis. Given this definition, the premise above requires that  $\Delta(p)$ , the upper bound on the scheduling of s, is at least as restrictive as the scheduling of any program point that may influence the presence or absence of activities running in parallel with pat the same place.

| T-Const                                                 | $T\text{-}Var$ $\mathcal{L}(\Gamma(x)) \sqsubseteq \mathcal{L}(Place$                                                                                                                                                                        | $ \begin{array}{c} \text{T-OP} \\ p; \Gamma; \Delta \vdash e_1 \\ p; \Gamma; \Delta \vdash e_2 \end{array} $                                                                                                | $\begin{array}{l} \textbf{T-READNONDET} \\ \Delta(p) \sqsubseteq \mathcal{L}(Place(p)) \end{array}$                                                                                                                    | $\begin{array}{c} \textbf{T-READDET} \\ \Delta(p) \not\sqsubseteq \mathcal{L}(Place(p)) \\ no Write(r,p) \end{array}$                                                                                                                                                       |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $p;\Gamma;\Delta\vdash v$                               | $p;\Gamma;\Delta\vdash x$                                                                                                                                                                                                                    | $p; \Gamma; \Delta \vdash e_1 \oplus e_2$                                                                                                                                                                   | $p; \Gamma; \Delta \vdash !r$                                                                                                                                                                                          | $p;\Gamma;\Delta\vdash !r$                                                                                                                                                                                                                                                  |

|                                                         | Fi                                                                                                                                                                                                                                           | gure 5. Expression typing                                                                                                                                                                                   | judgment $p; \Gamma; \Delta \vdash e$                                                                                                                                                                                  |                                                                                                                                                                                                                                                                             |

|                                                         | Ι                                                                                                                                                                                                                                            | SKIP2<br>$\begin{array}{l} & (p) \sqsubseteq \Delta(p) \sqsubseteq \Delta(p) \\ & (p' \in MHPA(p). \ \Delta(p') \sqsubseteq \Delta(p') \\ \hline & \Gamma; \Delta \vdash skip^p; s^{p_1}: \ell \end{array}$ | $\begin{array}{ccc} \Gamma_1 & & \Gamma; \Delta \vdash s_2 : \ell_2 & \Delta \\ \rho & & \forall p' \in MHF \end{array}$                                                                                               | $[x \mapsto Place(p)]; \Delta \vdash s_1 : \ell_1$<br>$\Delta(p) \sqsubseteq \Delta(p_1)  \ell_1 \sqsubseteq \Delta(p_2)$<br>$PA(p) : \Delta(p') \sqsubseteq \Delta(p)$<br>$x = e \text{ in } s_1^{p_1}; s_2^{p_2} : \ell_2$                                                |

| $\Delta(p) \sqsubseteq \Delta(p_2)$                     | $\begin{split} & \Gamma; \Delta \vdash s_2 : \ell_2 \qquad \Delta(p) \\ & \forall p' \in MHPA(p) . \ \Delta(p) \\ & \vdash async^p \ s_1^{p_1}; s_2^{p_2} : \ell_2 \end{split}$                                                              |                                                                                                                                                                                                             |                                                                                                                                                                                                                        | $\Delta(p_1)  \mathcal{L}(Place(p_2)) \sqsubseteq \Delta(p_2)$ $b' \in MHPA(p). \ \Delta(p') \sqsubseteq \Delta(p)$ $(s_2^{p_2}: \ell_2)$                                                                                                                                   |

|                                                         | $\Delta(p_1)$ $\ell_1 \sqsubseteq \Delta(p_2)$                                                                                                                                                                                               | $\vdash s_2 : \ell_2 \qquad \Delta(p) \sqsubseteq \mathcal{L}(P)$ $\forall p' \in MHPA(p). \ \Delta(p') \sqsubseteq$ $P \ s_1^{p_1}; s_2^{p_2} : \ell_2$                                                    | $\equiv \Delta(p) \qquad \qquad \forall p' \in M$                                                                                                                                                                      | $ \begin{array}{l} T \\ \mathfrak{s}: \ell & \Delta(p) \sqsubseteq \Delta(p_1) \\ HPA(p). \ \Delta(p') \sqsubseteq \Delta(p) \\ \vdash backat^p \ P; s^{p_1}: \ell \end{array} $                                                                                            |

|                                                         | TENONDET<br>$\Delta(p) \sqsubseteq \mathcal{L}(Place)$ $s: \ell \qquad p; \Gamma; \Delta \vdash e$ $\forall p' \in MHPA(p). \ \Delta(p')$ $\Gamma; \Delta \vdash r :=^{p} e; s^{p}$                                                          | $\Delta(p) \sqsubseteq \Delta(p_1)$ $) \sqsubseteq \Delta(p)$                                                                                                                                               | $ \frac{\text{T-WRITEDET}}{\Delta(p) \not\subseteq \mathcal{L}(Place(p))} \\ \Gamma; \Delta \vdash s : \ell \qquad p; \Gamma; \Delta \vdash \\ \frac{\forall p' \in MHPA(p) \cdot d}{\Gamma; \Delta \vdash r :=^{p}} $ | $e \qquad \Delta(p) \sqsubseteq \Delta(p_1) \\ \Delta(p') \sqsubseteq \Delta(p)$                                                                                                                                                                                            |

|                                                         | DUTNONDET<br>$\Delta(p) \sqsubseteq \mathcal{L}(Place)$ $s: \ell  p; \Gamma; \Delta \vdash e$ $\forall p' \in MHPA(p). \ \Delta(p')$ $\Gamma; \Delta \vdash output^p e; s$                                                                   | $\Delta(p) \sqsubseteq \Delta(p_1)$ $) \sqsubseteq \Delta(p)$                                                                                                                                               | $     \begin{aligned}       T-OUTPUTDET \\                                    $                                                                                                                                        | $e \qquad \Delta(p) \sqsubseteq \Delta(p_1) \\ \Delta(p') \sqsubseteq \Delta(p)$                                                                                                                                                                                            |

| $\Delta(p) \sqsubseteq \Delta(p_1)$                     | $\begin{array}{l} \overset{\mathrm{T}}{\mathcal{L}}(Place(p)) & \Gamma; \Delta \vdash \\ \forall p' \in MHPA(p). \ \Delta \\ \hline & \Gamma; \Delta \vdash input^p r; s^{p_1} : \ell \end{array}$                                           | (- <i>)</i>                                                                                                                                                                                                 | $\not\sqsubseteq \mathcal{L}(Place(p)) \qquad noRead$                                                                                                                                                                  | $\phi' \in MHPA(p). \ \Delta(p') \sqsubseteq \Delta(p)$                                                                                                                                                                                                                     |

| $p; \Gamma; \Delta$<br>$\ell_1 \sqsubseteq \Delta(p_3)$ | $\begin{split} s_1 &: \ell_1 & \Gamma; \Delta \vdash s_2 : \\ \Delta \vdash e & \Delta(p) \sqsubseteq \Delta(p_1) \\ \ell_2 \sqsubseteq \Delta(p_3) & \forall p' \in \\ \Gamma; \Delta \vdash if^p \ e \ then \ s_1^{p_1} \ els \end{split}$ | $ \Delta(p) \sqsubseteq \Delta(p_2) \in MHPA(p). \ \Delta(p') \sqsubseteq \Delta(p) $                                                                                                                       | $\begin{array}{c} \Delta(p) \sqsubseteq \Delta(p_1)  \ell \\ \forall p' \in MHPA \end{array}$                                                                                                                          | $\Delta \vdash s_{2} : \ell_{2} \qquad p_{1}; \Gamma; \Delta \vdash e$<br>$\ell_{1} \sqsubseteq \Delta(p) \qquad \ell_{1} \sqsubseteq \Delta(p_{2})$<br>$(p) \cdot \Delta(p') \sqsubseteq \Delta(p)$<br>$p^{p} e \operatorname{do} s_{1}^{p_{1}}; s_{2}^{p_{2}} : \ell_{2}$ |

**Figure 7.** Statement typing judgment  $\Gamma; \Delta \vdash s : \ell$

Also, almost all inference rules for statements ensure that if program point p executes after p' (for example, because they are in sequence), then  $\Delta(p') \sqsubseteq \Delta(p)$ . The intuition here is that if information at level  $\Delta(p')$  may influence the scheduling of p', and p follows in sequence after p', then information at level  $\Delta(p')$  may influence the scheduling of p. For example, the typing rule for if p e then  $s_1^{p_1}$  else  $s_2^{p_2}$ ;  $s_3^{p_3}$ requires that  $\Delta(p) \sqsubseteq \Delta(p_1)$  and  $\Delta(p) \sqsubseteq \Delta(p_2)$ , since the execution of  $s_1$  and  $s_2$  will occur only after the evaluation of the conditional guard. Similarly, since the execution of  $s_3$ will follow the execution of either  $s_1$  or  $s_2$ , the rule requires that  $\ell_1 \sqsubseteq \Delta(p_3)$  and  $\ell_2 \sqsubseteq \Delta(p_3)$ , where  $\ell_1$  and  $\ell_2$  are upper bounds of the scheduling of the last program points of  $s_1$  and  $s_2$  respectively.

We discuss only the inference rules that have premises in addition to those common to all rules.

Statement let x = e in  $s_1^{p_1}$ ;  $s_2^{p_2}$  declares a variable x, and allows x to be used in the scope of statement  $s_1$ . Rule T-LET thus allows  $s_1$  to be typed with a variable context that maps variable x to the place at which it was defined: Place(p).

Statement finish<sup>p</sup>  $s_1^{p_1}$ ;  $s_2^{p_2}$  executes statement  $s_1$ , and waits until all activities spawned by  $s_1$  have finished before executing  $s_2$ . Rule T-FINISH requires that  $\Delta(p) \sqsubseteq \Delta(p_1)$ (since  $p_1$  is executed after p) but notably does not require either  $\Delta(p) \sqsubseteq \Delta(p_2)$  or  $\ell_1 \sqsubseteq \Delta(p_2)$ , despite the fact that  $p_2$ is executed after p and  $p_1$ . The intuition is that because the scheduling behavior at place P = Place(p) depends only on the current activities at P, by the time that  $p_2$  is scheduled, program points p and  $p_1$  (and all activities spawned by  $s_1$ ) have finished execution, and do not influence the scheduling of  $p_2$ . In Program 3 in the Introduction, this reasoning is what permits us to conclude that the scheduling of output "B" and output "C" do not depend on high-security computation.

| 1  | at Low {                                           |

|----|----------------------------------------------------|

| 2  | async {                                            |

| 3  | // Activity 1                                      |

| 4  | <pre>mediumComputation(); output ''nonpos'';</pre> |

| 5  | }                                                  |

| 6  | finish {                                           |

| 7  | // Activity 2                                      |

| 8  | at High {                                          |

| 9  | if (hi > 0) longComputation();                     |

| 10 | }                                                  |

| 11 | }                                                  |

| 12 | // Activity 3                                      |

| 13 | output ''pos'';                                    |

| 14 | }                                                  |

| Program 4 | 4. |

|-----------|----|

|-----------|----|

However, it may be possible that scheduling of activities spawned by  $s_1$  indirectly influences the scheduling of  $p_2$ . Consider Program 4, which contains a finish  $s_1$ ;  $s_2$  statement where  $s_2 =$  output "pos", and  $s_1$  invokes computation at high-security place High. There is an additional activity that executes concurrently with the finish statement: mediumComputation(); output "nonpos". The scheduling of this activity relative to  $s_2$  will depend on the high-security computation. Indeed, this program is equivalent to Program 2, and both are insecure. Thus, typing rule T-FINISH requires that  $\Delta(p_2)$  is at least as restrictive as  $\Delta(p')$  for any program point p' that may execute in parallel with p at the same place. This ensures that insecure Program 4, and others like it, are rejected by the type system.

Statement at  $P P s_1^{p_1}$ ;  $s_2^{p_2}$  executes  $s_1$  at place P, and then executes  $s_2$  back at place Place(p). Rule T-AT requires that the upper bound on the scheduling of the at instruction is permitted to flow to the level of place  $P (\Delta(p) \sqsubseteq \mathcal{L}(P))$ . Thus the type system restricts the creation of an activity at place P to reveal only information that is allowed to flow to level  $\mathcal{L}(P)$ . Also, because statement  $s_1^{p_1}$  is executing at place P, information at level  $\mathcal{L}(P)$  will influence the scheduling of  $p_1: \mathcal{L}(P) \sqsubseteq \Delta(p_1)$ . Finally, because statement  $s_2^{p_2}$  is executed only after  $s_1$ , the scheduling of  $p_2$  depends on when the last statement of  $s_1$  is scheduled:  $\ell_1 \sqsubseteq \Delta(p_2)$  where  $\ell_1$  is an upper bound on the scheduling of the last program point of  $s_1$ .

Similar to the typing rules for reading memory locations, there are two rules for writing memory locations: T-WRITENONDET and T-WRITEDET. As with the rules for reading memory, the first is for the case where the scheduling of the write is not influenced by high-security information, and there are thus no restrictions on when the write may occur. Rule T-WRITEDET applies when the scheduling of the write may be influenced by high-security information, and requires observational determinism via the predicate noReadWrite(r, p), defined in Figure 6, which ensures that no reads or writes to the same memory location may happen in parallel.

The rules for input and output are similar to the rules for reading and writing memory locations: if the scheduling of input or output may depend on high-security information, the input or output must be observationally deterministic, which is achieved for output by requiring that there is no other input or output at that place that may happen in parallel (see predicate noIO(p), defined in Figure 6). Since an input instruction writes to a memory location r, rule T-INPUTDET requires both that no input or output may happen at the place in parallel, and that no reads or writes to r may happen in parallel.

**Typing trees** Judgment  $\Gamma; \Delta \vdash T$  means that tree T is well typed in variable context  $\Gamma$  and program point context  $\Delta$ . Inference rules for the judgment are given in Figure 8. The rules require that all activities in the tree are well typed. Also, the rule for tree  $T \triangleright \langle P, s^p \rangle$ , T-JOIN, requires that  $\Delta(p)$  is at least as restrictive as  $\Delta(p')$  for any program point p' that may execute in parallel with p at place P, for similar reasons to the typing rule for finish statements, T-FINISH.

| T-ACTIVITY                                                                  | T-PARA                                                 |  |  |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| $\Gamma; \Delta \vdash s : \ell  \mathcal{L}(P) \sqsubseteq \Delta(p)$      | $\Gamma; \Delta \vdash T_1  \Gamma; \Delta \vdash T_2$ |  |  |  |  |  |

| $\overline{\Gamma; \Delta \vdash \langle P, s^p \rangle}$                   | $\Gamma; \Delta \vdash T_1 \  T_2$                     |  |  |  |  |  |

|                                                                             |                                                        |  |  |  |  |  |

| T-JOIN                                                                      |                                                        |  |  |  |  |  |

| $\Gamma; \Delta \vdash T \qquad \Gamma; \Delta \vdash \langle P, s \rangle$ | p > T-DONE                                             |  |  |  |  |  |

| $\forall p' \in MHPP(p). \ \Delta(p') \sqsubseteq \Delta(p)$                | $\Delta(p)$                                            |  |  |  |  |  |

| $\Gamma; \Delta \vdash T \triangleright \langle P, s^p \rangle$             | $\Gamma; \Delta \vdash \checkmark$                     |  |  |  |  |  |

|                                                                             |                                                        |  |  |  |  |  |

**Figure 8.** Tree typing judgment  $\Gamma$ ;  $\Delta \vdash T$

*Soundness of type system* The type system enforces security. That is, if a program is well typed, then it is secure.

**Theorem 1.** If  $\langle P, s \rangle$  is a program such that  $\Gamma; \Delta \vdash \langle P, s \rangle$  for some variable context  $\Gamma$  and program point context  $\Delta$ , then  $\langle P, s \rangle$  is secure according to Definition 5.

We present a brief sketch of the proof here. A more detailed proof appears in Appendix A.

*Outline of Proof.* The proof uses a technique similar to that of Terauchi [44]. We first introduce the concept of an *erased configuration.* A configuration m erases to a configuration m' at security level  $\ell$  if m', when executed, performs no computation at places with security level higher than  $\ell$  but m and m' otherwise agree. Erased programs are defined similarly, with erased configurations containing erased programs.

Suppose we have a well-typed program  $\langle P, s \rangle$ , some security level  $\ell$ , and two  $\ell$ -equivalent input strategies  $\omega_1$  and  $\omega_2$ . First, we erase the program  $\langle P, s \rangle$  to program  $\langle P, s' \rangle$ at level  $\ell$  and consider side-by-side executions of these two programs with the same input strategy. Suppose the original program with input strategy  $\omega_1$  produces trace  $t_1$ . Then the erased program with input strategy  $\omega_1$  can produce a trace  $t'_1$ that is  $\ell$ -equivalent. Similarly, if the original program with input strategy  $\omega_2$  produces trace  $t_2$ , then the erased program with input strategy  $\omega_2$  can produce a trace  $t'_2$  that is  $\ell$ -equivalent.